Polytechnic Version

## **Quick Learner : Computer System Architecture**

Sharmilla binti Sulong | Adibah binti Ali Politeknik Kuala Tererngganu

#### **QUICK LEARNER : COMPUTER SYSTEM ARCHITECTURE**

First Published 2022 e ISBN 978-967-2240-35-8 Politeknik Kuala Terengganu

All rights reserved. No part of this electronic book may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying, recording or by any information storage or retrieval system, without prior written permission from the publisher, Politeknik Kuala Terengganu.

Published by : Politeknik Kuala Terengganu 20200 Jalan Sultan Ismail, Kuala Terengganu, Terengganu

Perpustakaan Negara Malaysia

Cataloguing-in-Publication Data

Sharmilla Sulong, 1977Quick Learner : Computer System Architecture / Sharmilla Binti Sulong,

Adibah Binti Ali. – Polytechnic Version.

Mode of access: Internet

eISBN 978-967-2240-35-8

1. Computer systems.

2. Computer architecture.

3. Computer organization.

4. Government publications--Malaysia.

5. Electronic books.

I. Adibah Ali, 1979-.

II. Title.

004

#### Abstract

This eBook designed for student to understand the basic concepts on which the stored program digital computer is formulated. The content of this eBook is written for polytechnic students.

This eBook introduces the basic knowledge of computer architecture and computer organization. It focuses on describing of function of each unit in Computer System in Chapter 1, applying appropriate method to solve arithmetic problem in numbering system and sequential logic circuit in Chapter 2, writing assembly program in Chapter 3 and foundation knowledge of Central Processing Unit in Chapter 4.

As there already many books written on computer architecture in the market, this eBook attempts to distinct itself by using mind mapping to help students visualize the concepts easily and practice drill after completing a topic. This allows students to better understand the topics they have learned while reinforcing existing skills. Therefore, this eBook helps students revise the topics taught in the classroom without having to read the notes that long and tedious.

It is hoped that this eBook will help both lecturer and students in making classroom learning as enjoyable as possible. This eBook can also be used for independent self-learning.

# Table of

**Chapter 1** The Computer System

14 Chapter 2 Number 5 Number Bases, Logic Gates & Flip Flop

**Chapter 3** 45

72

Assembly Language Chapter 4

62 Chapter 4 Central Processing Unit

### **Answer Scheme**

This chapter describes briefly the computer system.

#### Topic : The Computer System

#### Introduction

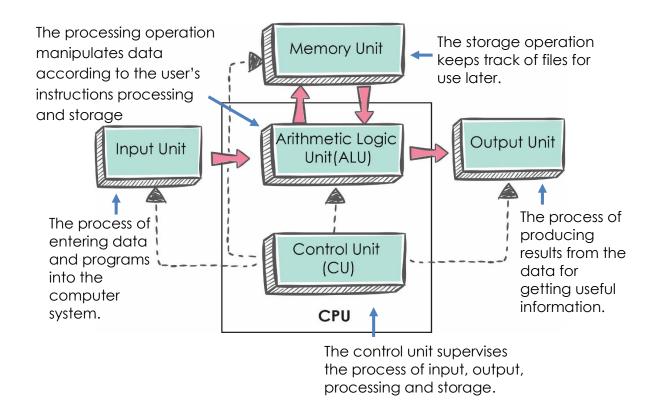

A computer system is a basic, complete and functional hardware and software setup with everything needed to implement computing performance. Computer System is a collection of entities (hardware, software and liveware) that are designed to receive, process, manage and present information in a meaningful format.

A computer system, therefore, is a computer combined with peripheral equipment and software so that it can perform desired functions. The components of a computer are designed to interact with one another, and this interaction plays an important role in the overall system operation.

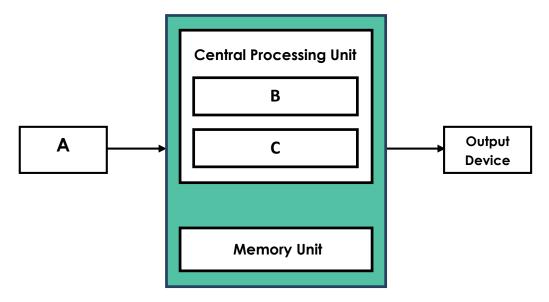

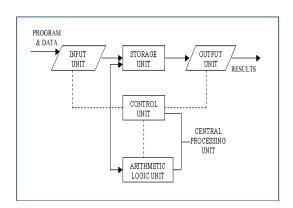

#### Block Diagram of Computer System

#### Computer Bus

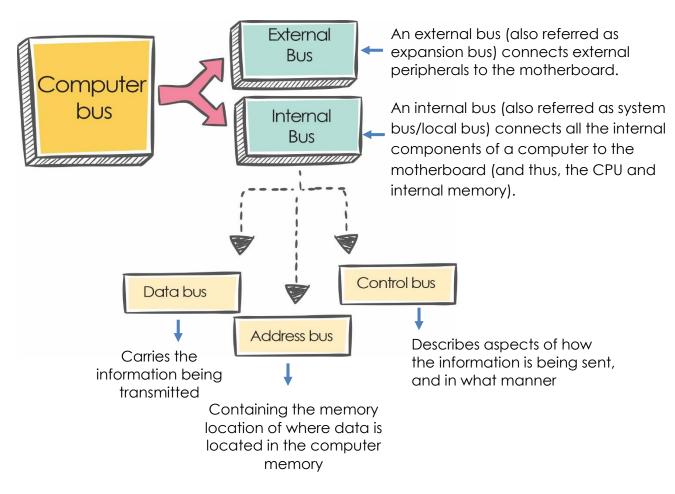

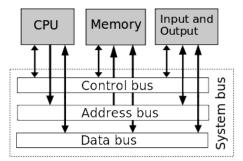

In computer architecture, a bus is a communication system that transfers data between components inside a computer, or between computers. Computer bus is a subsystem that transfers data between components inside a computer, or between computers.

The bus contains multiple wires with addressing information describing the **memory** location of where the data is sent or retrieved. Each wire in the bus carries a **bit(s)** of information, which means the more wires a bus has, the more information it can address.

#### Types of Bus

The most common buses and how they are used with a computer.

- **<u>eSATA</u>** and <u>SATA</u> Computer hard drives and disc drives.

- **<u>PCIe</u>** Computer expansion cards and video cards.

- **<u>USB</u>** Computer peripherals.

- **<u>Thunderbolt</u>** Peripherals connected through a USB-C cable.

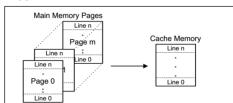

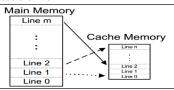

#### Cache

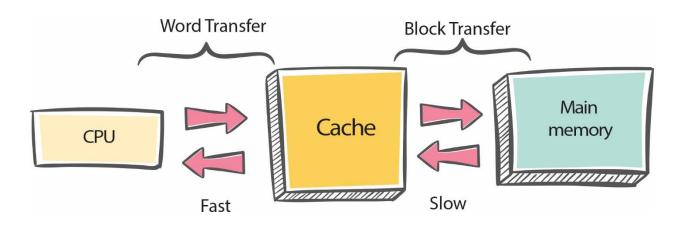

- A special very-high-speed memory called a cache, is used to increase the speed of processing by making current programs and data available to the CPU at a rapid rate.

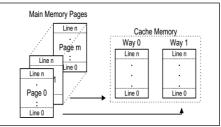

- The transformation of data from main memory to cache memory is called mapping. The mapping functions are used to map a particular block of main memory to a particular block of cache. This mapping function is used to transfer the block from main memory to cache memory.

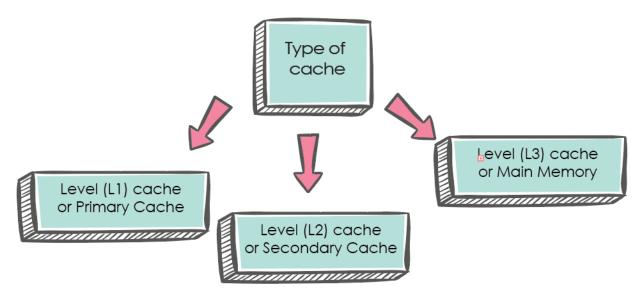

#### Type of Cache Memory

#### > Level 1 (L1) cache or Primary Cache

- the fastest memory that is present in a computer system

- The Size of the L1 cache very small comparison to others that is between 2KB to 64KB, it depends on computer processor.

- It is an embedded register in the computer microprocessor(CPU).

- The Instructions that are required by the CPU that are firstly searched in L1 Cache.

#### > Level 2 (L2) cache or Secondary Cache

- Slower than L1 cache, but bigger in size

- The size of the L2 cache is more capacious than L1 that is between 256KB to 512KB.

- L2 cache is Located on computer microprocessor.

- After searching the Instructions in L1 Cache, if not found then it searched into L2 cache by computer microprocessor.

#### > Level 3 (L3) cache or Main Memory

- The L3 cache is larger in size but also slower in speed than L1 and L2,

- It's size is between 1MB to 8MB.

- In Multicore processors, each core may have separate L1 and L2, but all core share a common L3 cache.

- L3 cache double speed than the RAM.

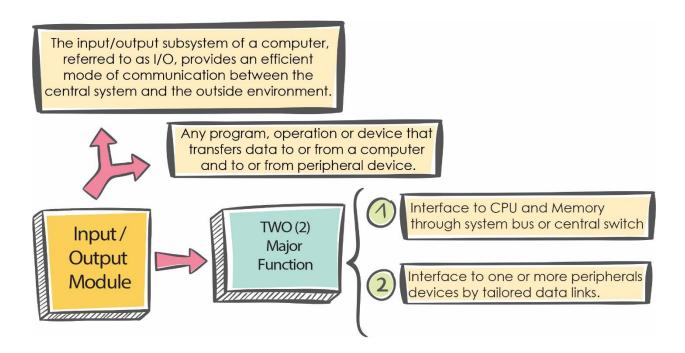

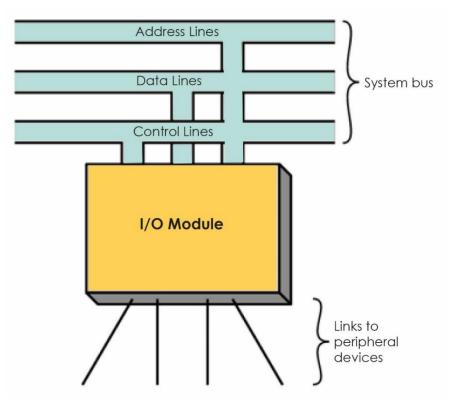

#### Input/Output Module

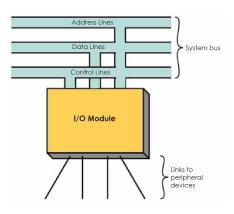

I/O module stands for Input/Output module, which is a device that acts as the connective bridge between a computer system at one end and an I/O or peripheral device of some kind at the other, such as a printer, webcam or scanner.

Input/Output Modules (I/O Modules) act as mediators between the processor and the input/output devices.

#### Generic Model of I/O Module

- Interface to CPU and Memory via system bus or central switch

- Interface to one or more peripherals devices by tailored data links.

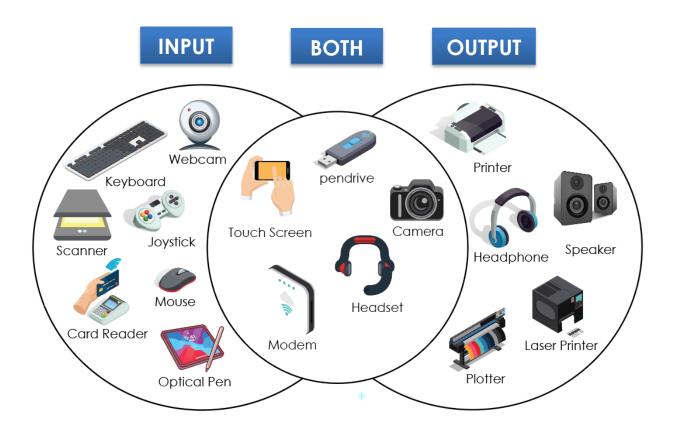

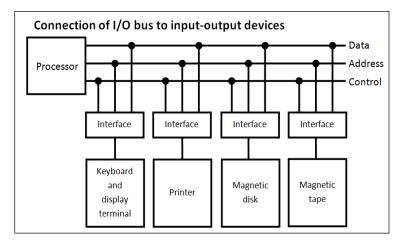

#### Input/Output Device

An input/output (I/O) device also called as **IO Device** is a hardware device that has the ability to accept **inputted**, **outputted** or **other processed** data.

IO devices allow the computer system to interact with the outside world by moving data into and out of the system. An **input device** is used to bring data into the system. An **output device** is used to send data out of the system.

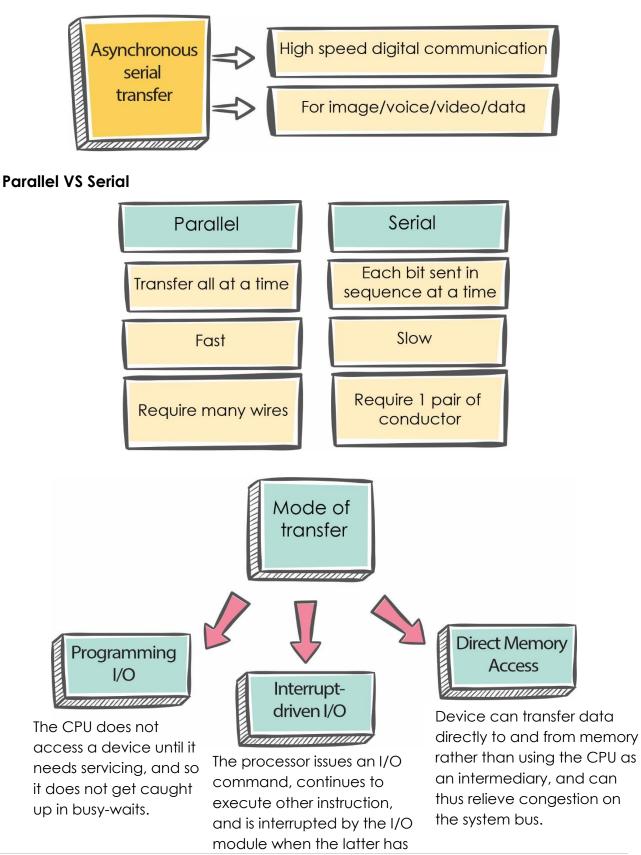

#### Asynchronous Serial Transfer

completed its work.

#### Activity 1

1. Draw a block diagram to illustrate the basic organization of computer system and describe the functions for each unit.

- 2. A bus is a communication pathway connecting two or more device. Describe the concept of interconnection within a computer system as follows :

- a. Draw interconnection structures

b. Describe the functions for each bus

3. Draw the I/O Module Diagram and explain how it works.

4. Describe the I/O bus and interface modules

#### Activity 2

Instruction : Answer all questions.

| I/O Module           | Programming I/O      | Address Bus | Data Bus |

|----------------------|----------------------|-------------|----------|

| Interrupt Driven I/O | Direct Memory Access | Control Bus | Tags     |

i. \_\_\_\_\_ carries the information being transmitted.

- ii. \_\_\_\_\_ identifies where the information is being sent.

- iii. \_\_\_\_\_ describes aspects of how the information is being sent, and in what manner.

- iv. With \_\_\_\_\_, data are exchanged between the processor and the I/O module.

- v. With \_\_\_\_\_, the processor issues an I/O command, continues to execute other instruction, and is interrupted by the I/O module when the latter has completed its work.

- vi. A \_\_\_\_\_\_ device can transfer data directly to and from memory rather than using the CPU as an intermediary.

- vii. Any program, operation or device that transfers data to or from a computer and to or from peripheral device is called \_\_\_\_\_\_.

- viii. \_\_\_\_\_ are used identify where cached data originated.

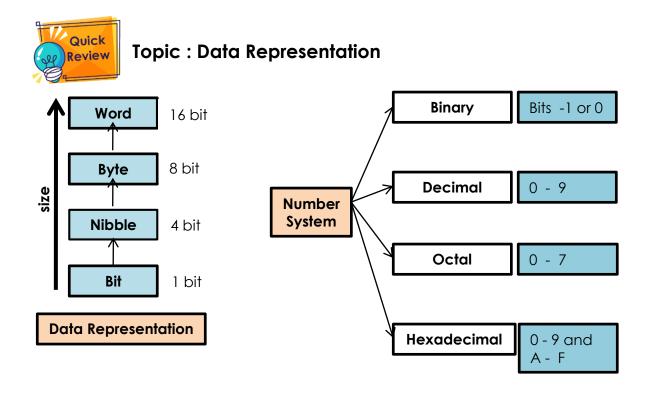

This chapter focuses on the method to solve arithmetic problem in numbering system and sequence logic circuit.

| 0         000           1         000           2         001           3         001           4         010           5         010           6         011           7         011           8         100           9         100           10         101           11         101 | 01<br>10<br>11<br>00<br>01<br>10<br>11 | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | numbers used in arithmetic<br>computations |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|--------------------------------------|--------------------------------------|--------------------------------------------|

| 2 001<br>3 001<br>4 010<br>5 010<br>6 011<br>7 011<br>8 100<br>9 100<br>10 101                                                                                                                                                                                                          | 10<br>11<br>00<br>01<br>10<br>11       | 3<br>4<br>5<br>6<br>7                | 3<br>4<br>5<br>6                     |                                            |

| 3         001           4         010           5         010           6         011           7         011           8         100           9         100           10         101                                                                                                  | 11<br>00<br>01<br>10<br>11             | 3<br>4<br>5<br>6<br>7                | 3<br>4<br>5<br>6                     |                                            |

| 4         010           5         010           6         011           7         011           8         100           9         100           10         101                                                                                                                          | 00<br>01<br>10<br>11                   | 4<br>5<br>6<br>7                     | 4<br>5<br>6                          |                                            |

| 5         010           6         011           7         011           8         100           9         100           10         101                                                                                                                                                  | 01<br>10<br>11                         | 5<br>6<br>7                          | 5<br>6                               |                                            |

| 6 011<br>7 011<br>8 100<br>9 100<br>10 101                                                                                                                                                                                                                                              | 10<br>11                               | 6<br>7                               | 6                                    |                                            |

| 7 011<br>8 100<br>9 100<br>10 101                                                                                                                                                                                                                                                       | 11                                     | 7                                    | -                                    | Data                                       |

| 8 100<br>9 100<br>10 101                                                                                                                                                                                                                                                                |                                        | ,                                    | 7                                    | Data /                                     |

| 9         100           10         101                                                                                                                                                                                                                                                  | 00                                     |                                      |                                      | Types Ietters of the alphabet used         |

| 10 101                                                                                                                                                                                                                                                                                  |                                        | 10                                   | 8                                    | stored in data processing                  |

|                                                                                                                                                                                                                                                                                         | 01                                     | 11                                   | 9                                    |                                            |

| 11 101                                                                                                                                                                                                                                                                                  | 10                                     | 12                                   | Α                                    |                                            |

|                                                                                                                                                                                                                                                                                         | 11                                     | 13                                   | В                                    | other discrete symbols                     |

| 12 110                                                                                                                                                                                                                                                                                  | 00                                     | 14                                   | С                                    | used for specific purposes                 |

| 13 110                                                                                                                                                                                                                                                                                  | 01                                     | 15                                   | D                                    |                                            |

| 14 111                                                                                                                                                                                                                                                                                  | 10                                     | 16                                   | E                                    |                                            |

| 15 111                                                                                                                                                                                                                                                                                  |                                        |                                      | F                                    |                                            |

One to One Comparison

Table : Conversion of Number System

| To<br>From  | DECIMAL                                    | BINARY                                                                                | OCTAL                                                                      | HEXADECIMAL                                                               |

|-------------|--------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------|

| DECIMAL     |                                            | Devide by 2                                                                           | Devide by 8                                                                | Devide by 16                                                              |

| BINARY      | Multiply<br>each bit by<br>2 <sup>n</sup>  |                                                                                       | -Group bit in<br>3's, starting<br>on right.<br>-Convert to<br>octal digit. | -Group bit in<br>4's, starting<br>on right.<br>-Convert to<br>hexa digit. |

| OCTAL       | Multiply<br>each bit by<br>8 <sup>n</sup>  | -Convert each<br>octal digit to a<br>3-bit<br>equivalent<br>binary<br>representation. |                                                                            | -Use a binary<br>as an<br>intermediary                                    |

| HEXADECIMAL | Multiply<br>each bit by<br>16 <sup>n</sup> | -Convert each<br>hexa digit to a<br>4-bit<br>equivalent<br>binary<br>representation.  | -Use a binary<br>as an<br>intermediary                                     |                                                                           |

#### Decimal to Binary, Octal, Hexadecimal

| Division<br>by 2                                                          | Quotient                                                                                      | Remainder                          |  | Division<br>By 8                                               | Quotient                                             | Remainder  |

|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------------------------|--|----------------------------------------------------------------|------------------------------------------------------|------------|

| 174/2                                                                     | 87                                                                                            | 0                                  |  | 1792/8                                                         | 224                                                  | 0          |

| 37/2                                                                      | 43                                                                                            | 1                                  |  | 224/8                                                          | 28                                                   | 0          |

| 13/2                                                                      | 21                                                                                            | 1                                  |  | 28/8                                                           | 3                                                    | 4          |

| 21/2                                                                      | 10                                                                                            | 1                                  |  | 3/8                                                            | 0                                                    | 3          |

| 0/2                                                                       | 5                                                                                             | 0                                  |  | 0                                                              | done.                                                |            |

| 5/2                                                                       | 2                                                                                             | 1                                  |  | So 1792 <sub>10</sub> =                                        | = <b>34</b> 00 <sub>8</sub>                          |            |

| 2/2                                                                       | 1                                                                                             | 0                                  |  |                                                                |                                                      |            |

|                                                                           |                                                                                               |                                    |  |                                                                |                                                      |            |

| 0 174 <sub>10</sub> =                                                     | 0<br>101011102                                                                                |                                    |  | Convert                                                        | 0 4875) +                                            | - bingny : |

| 0 174 <sub>10</sub> =                                                     | 101011102                                                                                     |                                    |  | _                                                              | 0.6875)10 to                                         | o binary : |

| o 174 <sub>10</sub> =<br>onvert 1<br>Division                             | 101011102                                                                                     |                                    |  | 0.6875 x 2<br>0.3750 x 2<br>0.7500 x 2                         | 2 = 1.3750<br>2 = 0.7500<br>2 = 1.5000               | o binary : |

| onvert 1<br>Division<br>By 16                                             | 10101110 <sub>2</sub>                                                                         | exadecima                          |  | 0.6875 x 2<br>0.3750 x 2<br>0.7500 x 2<br>0.5000 x 2           | 2 = 1.3750<br>2 = 0.7500<br>2 = 1.5000               | o binary : |

| o 174 <sub>10</sub> =<br>onvert 1<br>Division<br>By 16<br>792/16          | 101011102                                                                                     | <b>exadecima</b><br>Remainder      |  | 0.6875 x 2<br>0.3750 x 2<br>0.7500 x 2<br>0.5000 x 2<br>0.0000 | 2 = 1.3750<br>2 = 0.7500<br>2 = 1.5000<br>2 = 1.0000 | o binary : |

| o 174 <sub>10</sub> =<br>onvert 1<br>Division<br>3y 16<br>792/16<br>12/16 | 101011102                                                                                     | <b>exadecima</b><br>Remainder<br>0 |  | 0.6875 x 2<br>0.3750 x 2<br>0.7500 x 2<br>0.5000 x 2           | 2 = 1.3750<br>2 = 0.7500<br>2 = 1.5000<br>2 = 1.0000 | o binary : |

|                                                                           | 101011102<br>79210 to h<br>Quotient<br>112<br>7                                               | exadecima<br>Remainder<br>0<br>0   |  | 0.6875 x 2<br>0.3750 x 2<br>0.7500 x 2<br>0.5000 x 2<br>0.0000 | 2 = 1.3750<br>2 = 0.7500<br>2 = 1.5000<br>2 = 1.0000 | o binary : |

| Division<br>By 16<br>792/16<br>12/16                                      | <b>10101110</b><br><b>792</b> <sub>10</sub> <b>to h</b><br>Quotient<br>112<br>7<br>0<br>done. | exadecima<br>Remainder<br>0<br>0   |  | 0.6875 x 2<br>0.3750 x 2<br>0.7500 x 2<br>0.5000 x 2<br>0.0000 | 2 = 1.3750<br>2 = 0.7500<br>2 = 1.5000<br>2 = 1.0000 | o binary : |

#### Binary to Octal, Decimal and Hexadecimal

| binary<br>number:111001power<br>of 2:252423222120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 111 001<br>7 1<br>Octal: 0 1 2 3 4 5 6 7<br>Binary: 000 001 010 011 100 101 110 111                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $1 \cdot 2^{5} + 1 \cdot 2^{4} + 1 \cdot 2^{3} + 0 \cdot 2^{2} + 0 \cdot 2^{1} + 1 \cdot 2^{0}$<br>= 57 <sub>10</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                   |

| Binary:       0000       0011       0100       0101       0110       0111         Hexadecimal:       0       1       2       3       4       5       6       7         Binary:       1000       1001       1010       1011       1100       1111       1111       1111         Hexadecimal:       8       9       A       B       C       D       E       F         0011       1001       3       9       3       9       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S       S </th <td>Convert <math>(101.01)_2</math> to decimal:<br/>1 0 1. 0 1<br/><math>\downarrow \downarrow \downarrow \downarrow \downarrow \downarrow \downarrow</math><br/><math>2^2 2^1 2^0 2^{-1} 2^{-2}</math><br/><math>4+0+1+0+1/2^2 = 5.25</math><br/><math>(101.01)_2 \rightarrow (5.25)_{10}</math></td> | Convert $(101.01)_2$ to decimal:<br>1 0 1. 0 1<br>$\downarrow \downarrow \downarrow \downarrow \downarrow \downarrow \downarrow$<br>$2^2 2^1 2^0 2^{-1} 2^{-2}$<br>$4+0+1+0+1/2^2 = 5.25$<br>$(101.01)_2 \rightarrow (5.25)_{10}$ |

#### Octal to Binary, Decimal and Hexadecimal

| <b>Convert 37</b> <sub>8</sub> to decimal :<br>$3 \times 8^{1} + 7 \times 8^{0} = 24 + 7 = 31$<br>So $37_{8} = 31$ | Convert 37 <sub>8</sub> to binary :<br>Octal: 0 1 2 3 4 5 6 7<br>Binary: 000 001 010 011 100 101 110 111<br>3 7<br>011 111<br>So 37 <sub>8</sub> = 011111 <sub>2</sub> |

|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Convert $37_{b}$ to hexadecimal:                                                                                   | <b>Convert 37. 45to binary :</b><br><b>3 7 4 5</b><br>011 111 100 101<br>So 37. 458 = 011111.1001012                                                                   |

#### Hexadecimal to Binary, Decimal and Octal

| $= (7 * 16^{2}) + (13 * 16^{1}) + (14 * 16^{0})$ $= (7 * 256) + (13 * 16) + (14 * 1) = (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (100 + 10^{1}) + (10$ | Convert 7DE <sub>16</sub> to decimal:                        | Convert 7DE <sub>16</sub> to binary :                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| The second state       The second state       The second state         1.       The second state       The second state         2.       The second state       The second state         3.       The second state       The second state         0.111.1110.11110       The second state       The second state         0.111.1110.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $(14 * 16^{\circ})$<br>= (7 * 256) + (13 * 16) +<br>(14 * 1) | Hexadecimal:         8         9         A         B         C         D         E         F           Binary:         1000         1001         1010         1011         1100         1101         1111           Hexadecimal:         8         9         A         B         C         D         E         F |

| 1.       7       D       E         0111       1101       1110         2.       011       111       011       110         3       7       3       6       So       7DE.       1A16 =         01111101110       000110102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                              | So 7DE <sub>16</sub> = 011111011110 <sub>2</sub>                                                                                                                                                                                                                                                                 |

| $1.$ $2.$ $0111$ $1101$ $1110$ $0111$ $1101$ $1110$ $0001$ $1010$ $2.$ $0111$ $1111$ $0111$ $1101$ $1110$ $0001$ $1010$ $2.$ $0111$ $1111$ $0111$ $1100$ $0001$ $1010$ $3.$ $7.$ $3.6$ $6.$ $011111011110.00011010_2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Convert 7DE16 to Octal :                                     | Convert 7DE. 1A16 to binary :                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $\begin{array}{cccccccccccccccccccccccccccccccccccc$         | 0111 1101 1110 0001 1010<br>So <b>7DE. 1A</b> 16 =                                                                                                                                                                                                                                                               |

#### Sign Addition In 2's Complement

#### Example 1 :

#### Example 2 :

| + 6 | 00000110         | - 6 | <mark>1</mark> 1111010 |

|-----|------------------|-----|------------------------|

| +13 | 0 <u>0001101</u> | +13 | 0 <u>0001101</u>       |

| +19 | 00010011         | +7  | 00000111               |

#### Example 3 :

Example 4 :

| +6          | 00000110 | -6         | 11111010               |

|-------------|----------|------------|------------------------|

| - <u>13</u> | 11110011 | <u>-13</u> | 1 <u>1110011</u>       |

| -7          | 11111001 | -19        | <mark>1</mark> 1101101 |

#### **Overflow Example :**

| +70  | 0 1000110 | -70        | 1 0111010        |

|------|-----------|------------|------------------|

| +80  | 0 1010000 | -80        | <u>1 0110000</u> |

| +150 | 1 0010110 | -150 01101 | 010              |

\*\* An overflow may occur if the two numbers added are both either positive or negative.

#### Arithmetic Operation In Different Number Bases

#### Binary Coded Decimal (BCD) or 8421 Code

The binary coded decimal code, abbreviated as BCD, is a method that uses binary digits "0" and "1". ON state represents "1" and OFF state represents "0". Each digit is called a bit. This coding system has been used since the first computer. This coding system deals with decimal and binary numbers. Each decimal number requires 4 bits to code them.

BCD is a decimal number with each **digit encoded** to its **binary equivalent**. **Each digit** of a decimal is represented by its **four-bit binary equivalent** (1 to 9). A BCD number is **not** the same as a straight binary number. The primary advantage of BCD is the **relative ease of converting** to and from decimal.

a) Convert the number 874,10 to BCD 8421:

| 8    | 7    | 4    | (decimal) |

|------|------|------|-----------|

| 1000 | 0111 | 0100 | (BCD)     |

874<sub>10</sub> = 1000 0111 0100<sub>BCD8421</sub>

| b) Convert <b>0110100000111001<sub>BCD</sub></b> to decimal |

|-------------------------------------------------------------|

|-------------------------------------------------------------|

| 0110 | 1000 | 0011 | 1001 |

|------|------|------|------|

| 6    | 8    | 3    | 9    |

**0110100000111001**<sub>BCD</sub> = 6839<sub>10</sub>

#### Activity 1

- 1. Perform arithmetic operations (additional and subtraction) in different number base.

- i) Perform the following additional in the binary number system.

| a) 1101101 <sub>2</sub> + 1010 <sub>2</sub> | b) 1001 <sub>2</sub> + 111 <sub>2</sub>   |

|---------------------------------------------|-------------------------------------------|

|                                             | 0) 10012 + 1112                           |

| c) 1100 <sub>2</sub> + 101 <sub>2</sub>     | d) 11111 <sub>2</sub> + 1111 <sub>2</sub> |

|                                             |                                           |

| e) 356 <sub>8</sub> + 176 <sub>8</sub>      | f) AB8916 + ABCD16                        |

| ii) | Perform the following subtractions in the binary number system. |

|-----|-----------------------------------------------------------------|

| 11) | Perform the following subfractions in the bindry number system. |

| ,   |                                                                 |

| α) 1101 <sub>2</sub> 110 <sub>2</sub>  | b) 1100 <sub>2</sub> - 101 <sub>2</sub>   |

|----------------------------------------|-------------------------------------------|

| c) 1001 <sub>2</sub> – 11 <sub>2</sub> | d) 10001 <sub>2</sub> - 1011 <sub>2</sub> |

| e) 726 <sub>8</sub> - 473 <sub>8</sub> | f) ABCF <sub>16</sub> – 6ED <sub>16</sub> |

- 2. Convert binary, octal and hexadecimal numbers to different bases and vice-versa.

- i) Convert each of the following binary numbers into its equivalent in the octal and hexadecimal.

| a) 1110 <sub>2</sub>       | b) 101011010 <sub>2</sub>   |

|----------------------------|-----------------------------|

| C) 1010001011 <sub>2</sub> | d) 11100100110 <sub>2</sub> |

| e) 11011010 <sub>2</sub>   | f) 11111110 <sub>2</sub>    |

| a) 37 <sub>8</sub> | b) 724 <sub>8</sub> |

|--------------------|---------------------|

|                    |                     |

|                    |                     |

|                    |                     |

|                    |                     |

|                    |                     |

|                    |                     |

|                    |                     |

| c) 61 <sub>8</sub> | d) 45 <sub>8</sub>  |

| -,                 |                     |

|                    |                     |

|                    |                     |

|                    |                     |

|                    |                     |

|                    |                     |

|                    |                     |

|                    |                     |

|                    |                     |

| e) 71.458          | f) 23.1468          |

|                    |                     |

|                    |                     |

|                    |                     |

|                    |                     |

|                    |                     |

|                    |                     |

|                    |                     |

|                    |                     |

ii) Convert each of the following octal numbers into its equivalent in the binary number.

iii) Convert each of the following hexadecimal numbers into its equivalent in the binary number.

| a) 1C <sub>16</sub> | b) F2 <sub>16</sub>  |

|---------------------|----------------------|

| c) 4516             | d) 8EA <sub>16</sub> |

| e) ABC.1216         | f) 47.5B16           |

#### Activity 2

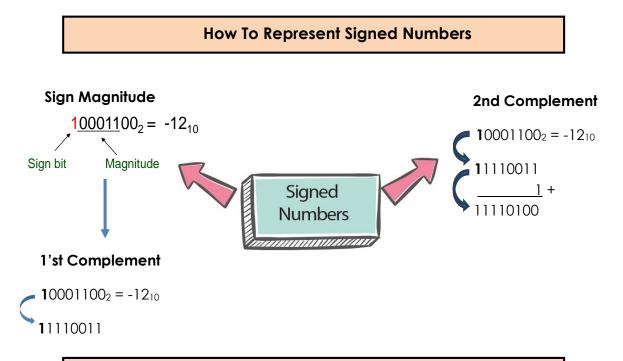

1. Show the number below to sign magnitude, 1's complement and 2's complement.

| Number    | Sign Magnitude | 1's Complement | 2's Complement |

|-----------|----------------|----------------|----------------|

| i. + 17   |                |                |                |

|           |                |                |                |

|           |                |                |                |

|           |                |                |                |

|           |                |                |                |

|           |                |                |                |

| ii. – 45  |                |                |                |

|           |                |                |                |

|           |                |                |                |

|           |                |                |                |

|           |                |                |                |

|           |                |                |                |

|           |                |                |                |

| iii. – 34 |                |                |                |

|           |                |                |                |

|           |                |                |                |

|           |                |                |                |

|           |                |                |                |

|           |                |                |                |

2. Solve the problem below by using 2<sup>nd</sup> complement:

a. 45 - 26

b. -17 + 19

c. 7A<sub>16</sub>-15<sub>16</sub>

3. Write the following decimal numbers into BCD 8421 code.

i. 2573

ii. 9287

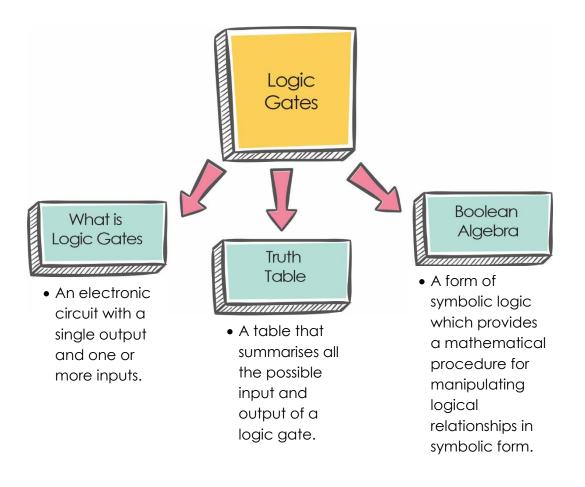

#### **Topic : Logic Gates**

Boolean algebra is a mathematical system operating on binary digits or bits specifically 0's and 1's. They perform several mathematical operations. Digital circuits that have one or more inputs, but only one output that can perform logical operations are called logic gates.

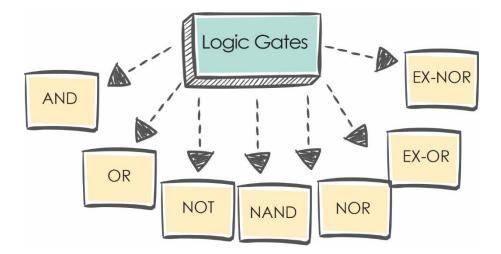

# **Basic Logic Gates**

| Туре | Symbol            | Boolean Algebra | Truth Table  |

|------|-------------------|-----------------|--------------|

|      | (                 |                 | Input Output |

|      |                   |                 | A B X        |

| AND  |                   |                 | 0 0 0        |

|      |                   | Y = A . B       | 0 1 0        |

|      |                   |                 | 1 0 0        |

|      |                   |                 |              |

|      |                   |                 | Input Output |

|      | 1                 |                 | A B X        |

| OR   | $\neg  ightarrow$ |                 | 0 0 0        |

|      |                   | Y = A + B       | 0 1 1        |

|      |                   |                 | 1 0 1        |

|      |                   |                 | 1 1 1        |

|      |                   |                 | Input Output |

| NOT  |                   | _               | A X          |

| NOT  | ≫_                | Y = A           | 0 1          |

|      |                   |                 | 1 0          |

|      |                   |                 |              |

# **Combinational Logic Gates**

| Туре   | Symbol      | Boolean Algebra            |     | •      | Truth 1 | ſable  |   |

|--------|-------------|----------------------------|-----|--------|---------|--------|---|

|        |             |                            |     | Inp    | out     | Output |   |

|        |             |                            |     | Α      | В       | X      |   |

| NAND   |             | <u> </u>                   |     | 0      | 0       | 1      |   |

|        |             | Y = A + B                  |     | 0      | 1       | 1      |   |

|        |             |                            | _   | 1      | 0       | 1      |   |

|        |             |                            |     | 1      | 1       | 0      |   |

|        |             |                            |     | Ing    | out     | Output | 1 |

|        |             |                            | Ī   | Α      | В       | X      |   |

| NOR    |             |                            | Ī   | 0      | 0       | 1      |   |

|        | <i>&gt;</i> | $Y = \overline{A \cdot B}$ |     | 0      | 1       | 0      |   |

|        |             |                            |     | 1      | 0       | 0      |   |

|        |             |                            |     | 1      | 1       | 0      |   |

|        |             | Y = A + B                  | out | Output |         |        |   |

|        | _H          |                            |     | Α      | В       | Х      |   |

| EX-OR  |             |                            |     | 0      | 0       | 0      |   |

|        |             |                            |     | 0      | 1       | 1      |   |

|        |             |                            | _   | 1      | 0       | 1      |   |

|        |             |                            |     | 1      | 1       | 0      |   |

|        |             |                            |     | Inp    | out     | Output |   |

|        | -           |                            |     | Α      | В       | Х      |   |

| EX-NOR | / <i>D</i>  | Y = A + B                  |     | 0      | 0       | 1      |   |

|        |             |                            |     | 0      | 1       | 0      |   |

|        |             |                            |     | 1      | 0       | 0      |   |

|        |             |                            |     | 1      | 1       | 1      | ] |

Exercises 1 - 6 are short answer or design questions.

- 1. Differentiate between a gate and a circuit.

- 2. Notational methods are used for describing the behavior of gates and circuits. Identify the three of notational methods and describe about the notations.

- 3. How many input signals can a gate receive and output signals can a gate produce?

- 4. Give the three notation or representations of a NOT gate.

#### Activity 2

Exercises 1-10, mark the answers True or False :

| 1.  | Logic diagrams and truth tables are equally powerful in expressing    |  |

|-----|-----------------------------------------------------------------------|--|

|     | the processing of gates and circuits.                                 |  |

| 2.  | Boolean expressions are more powerful than logic diagrams in          |  |

|     | expressing the processing of gates and circuits.                      |  |

| 3.  | A NOT gate accepts two inputs.                                        |  |

| 4.  | The output value of an AND gate when both inputs are 1 is 1.          |  |

| 5.  | The AND and OR gates produce opposite results for the same input      |  |

| 6.  | The output value of an OR gate when both inputs are 1 is 1.           |  |

| 7.  | The output of an OR gate when one input is 0 and one input is 1 is 0. |  |

| 8.  | The output value of an XOR gate is 0 unless both inputs are 1.        |  |

| 9.  | The Active High gate produces the opposite results of the XOR gate.   |  |

| 10. | A gate can be designed to accept more than two inputs.                |  |

For Exercises 1 - 12, match the gate with the diagram or description of the operation.

- A. AND

- B. OR

- C. NOT D. NAND

- E. NOR

- F. XOR

| 1.  | Inverts its input.                                              |  |

|-----|-----------------------------------------------------------------|--|

| 2.  | Produces a 1 only if all its inputs are 1 and a 0 otherwise.    |  |

| 3.  | Produces a 0 only if all its inputs are 0 and a 1 otherwise.    |  |

| 4.  | Produces a 0 only of its inputs are the same and a 1 otherwise. |  |

| 5.  | Produces a 0 of all its inputs are all 1 and a 1 otherwise.     |  |

| 6.  | Produces a 1 if all its inputs are 0 and a 0 otherwise.         |  |

| 7.  | AX                                                              |  |

| 8.  | A X<br>B                                                        |  |

| 9.  | A<br>B<br>X                                                     |  |

| 10. |                                                                 |  |

| 11. | A X<br>B                                                        |  |

| 12. |                                                                 |  |

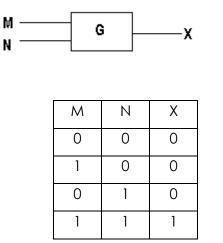

1. The diagram shows a logic gate G whose truth table is a shown in the table below.

Answer : \_\_\_\_\_

2. A NOR gate with input signals M = 01010101 and N = 011010100. What is the output signal of the logic gate.

Answer : \_\_\_\_\_

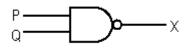

3. The figure shows a logic gate with inputs P and Q.

If the input P = 0011010 and the input Q = 1100011, what is the output X?

Answer : \_\_\_\_\_

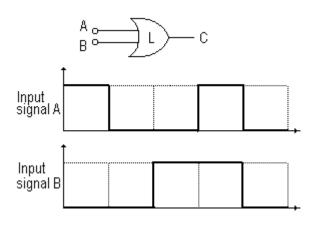

4. The diagram shows a logic gate ,L with input signals A and B.

(i) Name the logic gate L.

.....

(ii) Draw the output signal C in the graph below.

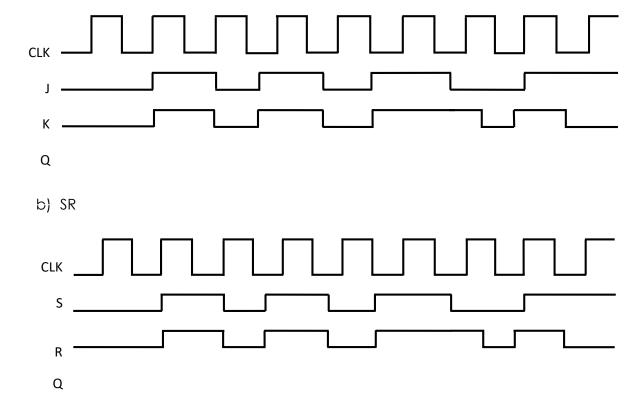

## **Topic : Flip Flop**

### **Sequential Logic Circuit**

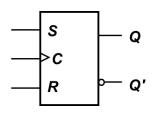

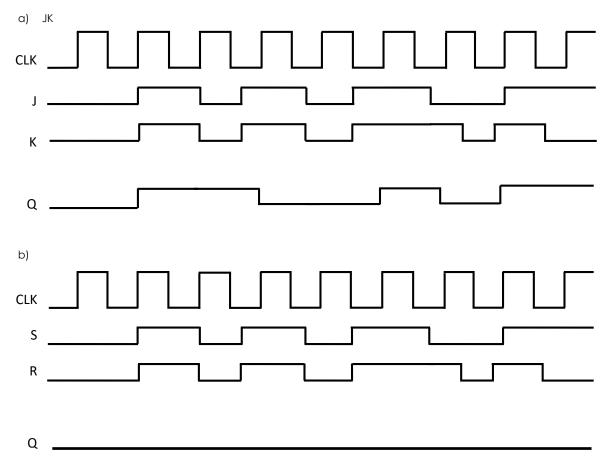

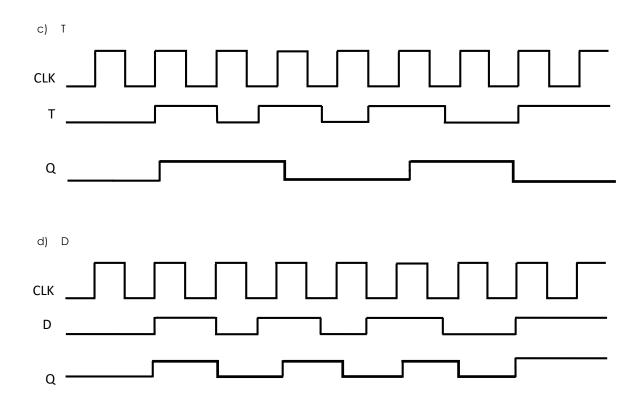

Sequential logic circuit is a memory property circuit and have output that depend on the previous output(s) and current inputs. In order to provide the previous input or output a memory element is required to be used. Thus a sequential circuit needs memory element. Also required clock input.

In general, a sequential circuit is synchronised by the clock signal (pulse) – synchronised circuit. The basic block diagram for a sequential circuit is memory device called *flip-flop* that consist of 2 stable operational states (outputs) Q and  $\bar{Q}$ . Flip-flop is a circuit that has two stable states and can be used to store state information.

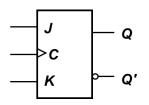

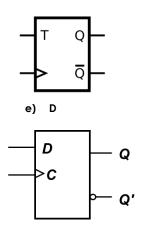

| ТҮРЕ                                             | LOGIC GATES                                  | TRUTH TABLE                                                                                                                                                                                                                                                                                | TIMING DIAGRAM                                             |

|--------------------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| NOR<br>GATES SR<br>FLIP FLOP<br>(active<br>HIGH) | R (reset)                                    | SROperation00No Change01Reset10Set11Invalid                                                                                                                                                                                                                                                |                                                            |

| NAND<br>GATES SR<br>FLIP FLOP<br>(active<br>LOW) | S(set)<br>R(reset)                           | SROperation00Invalid01Reset10Set11No Change                                                                                                                                                                                                                                                | S<br>R<br>Q<br>11<br>T2<br>T3<br>T4<br>T5<br>T6            |

| Clocked<br>SR                                    | R (reset )<br>CP<br>(doci pulse)<br>S (set ) | Inp∪t         CLK         Output           S         R         Q           0         0         1         Not<br>Changing           0         1         1         0           1         0         1         1           1         1         1         invalid                               | CLK 1 2 3 4 5 6<br>S 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 7 |

| JK FLIP<br>FLOP                                  |                                              | Input         Clock         Output           J         K         Q           0         0         1         No           0         1         1         O           0         1         1         0           1         0         1         1           1         1         1         Toggle | CLK 1 2 3 4 5<br>J K J Change Reset Set Set                |

| t flip<br>flop                                   |                                              | Clock         I         Q <sub>x+1</sub> 1         0         Q           1         1         Q                                                                                                                                                                                             |                                                            |

| D FLIP |              | · • |     |       | <u> </u> |   |

|--------|--------------|-----|-----|-------|----------|---|

| FLOP   |              | Inp | out | Clock | Output   |   |

|        | CP CP        | S   | R   |       | Q        |   |

|        | (dock pulse) | 0   | 0   | 1     | Not      |   |

|        |              |     |     |       | Changing |   |

|        |              | 0   | 1   | 1     | 0        |   |

|        |              | 1   | 0   | 1     | 1        | Q |

|        |              | 1   | 1   | 1     | invalid  |   |

|        |              |     |     |       |          |   |

|        |              |     |     |       |          |   |

1. Draw the logic symbols and develop truth tables of each given flip flop below.

2.

a) SR (NOR GATE)

b) Clocked SR

c) JK

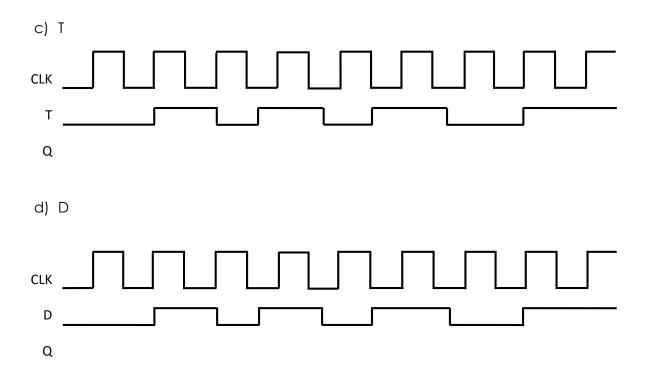

1. Draw the timing diagram of JK, Clocked SR, T and D flip-flop a) JK

e) D

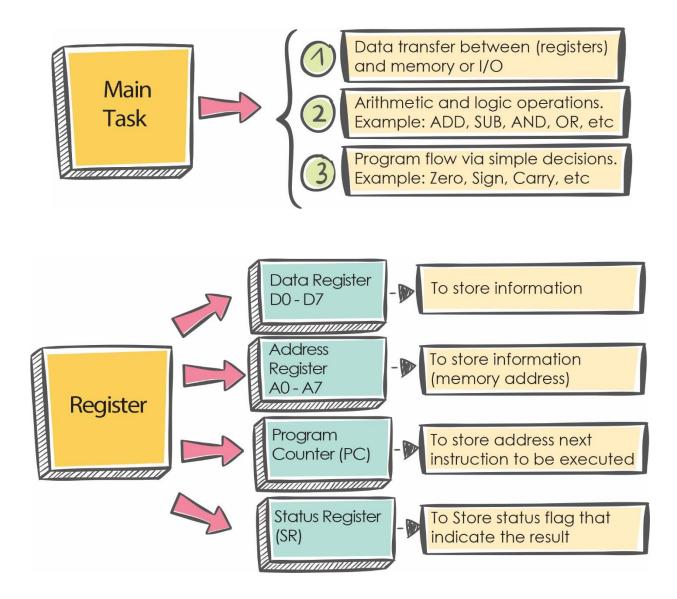

This chapter describes briefly about assembly language

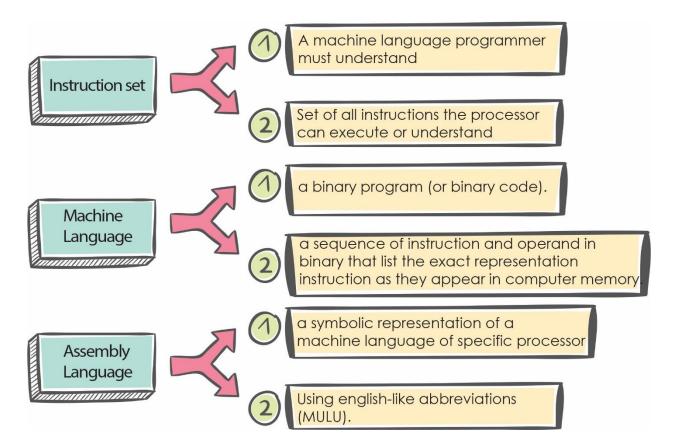

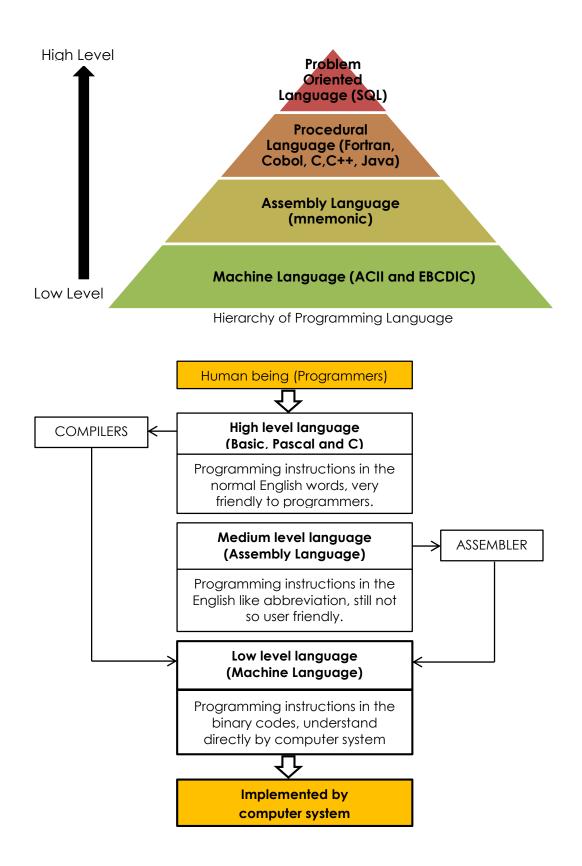

### Instruction Set, Machine And Assembly Language

### Basic Information of Microprocessor Motorola 68000

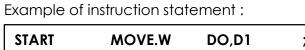

### Instruction and Data Format

#### Instruction Format

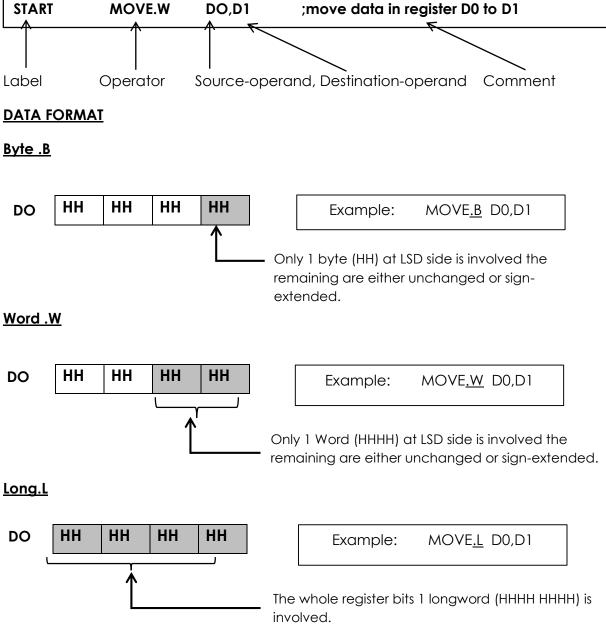

# Data Types

### Types of Addressing Modes

| Implicit / Implied             | RTS              |

|--------------------------------|------------------|

| Immediate                      | MOVE.B #\$40,D0  |

|                                | MOVE.W #40,D5    |

|                                | MOVE.L #\$30, D7 |

| Absolute                       | MOVE.B \$7000,D3 |

|                                | MOVE.L D4,\$1234 |

| Data Register Direct           | MOVE.L D0,D7     |

| Address Register Direct        | MOVE.L A3,A1     |

|                                | MOVE.L A4,D5     |

| Address Register Indirect      | MOVE.L D2, (A0)  |

|                                | MOVE.W (A3),D7   |

| Address Register Indirect with | MOVE.W –(A6),D0  |

| Predecrement                   |                  |

| Address Register Indirect with | MOVE.W (A6)+,D0  |

| Postincrement                  |                  |

# Example of Instruction in Various Types of Addressing Modes

| DATA TRANSFER                                                                                                                                                                                                                                                                               | ARITHMETIC AND LOGIC OPERATION                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Example 1 :                                                                                                                                                                                                                                                                                 | Example 1 :                                                                                                         |

| MOVE.W #\$72,D1<br>Before : D1 = \$00200500<br>After : D1 = \$00200072                                                                                                                                                                                                                      | ADD.B D0, D1<br>Before : D0 = \$00002222 , D1 = \$00004444<br>After : D0 = \$00002222 , D1 = \$00204466             |

| Example 2 :                                                                                                                                                                                                                                                                                 | Example 2 :                                                                                                         |

| MOVE.B D0,D1<br>Before : D1 = \$00200500 , D0 = \$00002222<br>After : D1 = \$00200522 , D0 = \$00002222                                                                                                                                                                                     | SUB.W #\$80,D3<br>Before : D3 = \$AB206541<br>After : D3 = \$AB2064C1                                               |

| Example 3:                                                                                                                                                                                                                                                                                  | Example 3 :                                                                                                         |

| MOVE.B \$3000,D1<br>Before : D1 = \$00200500<br>After : D1 = \$00200532                                                                                                                                                                                                                     | MULU #2,D2<br>Before : D2 = \$AB20FFFF<br>After : D2 = \$0001FFFE                                                   |

| \$3000         32           \$3001         43           \$3002         98                                                                                                                                                                                                                   | Example 4 :<br>AND.B #\$3E,D1<br>Before : D1 = \$12345674<br>After : D1 = \$12345634                                |

| Example 4:<br>MOVE.W D6,\$4000<br>Before: D6 = \$AB206541<br>After : D6 = \$AB206541                                                                                                                                                                                                        | 74 0111 0100<br>3E <u>0011 1110</u> &&<br>0011 0100<br>3 4                                                          |

| \$4000       3254       \$4000       32         \$4002       4377       @ \$4001       54         \$4004       9868       \$4002       43         \$4000       6541       \$4000       65         \$4002       4377       @ \$4001       41         \$4004       9868       \$4002       43 | Example 5 :<br>NOT.B D1<br>Before : D1 = \$12345655<br>After : D1 = \$123456AA<br>55 01010101<br>1010 1010 !<br>A A |

#### **Assembly Program**

#### FORMAT OF WRITING ASSEMBLY PROGRAM

ORG \$1000 - PC Loaded With \$1000, Start executing from here

,-----

PROGRAM INSTRUCTION

END \$1000 - Ending of the program

\_\_\_\_\_

Example 1 :

A program that add 25 and 34.

ORG \$1000 MOVE.B #25, D0 MOVE.B #34, D1 ADD.B D0,D1 END \$1000

Example 2 :

A program that solve the expression

! ( 4000<sub>8</sub> + 10111010<sub>2</sub> / ACEF<sub>16</sub>) ORG \$1000 MOVE.L #@4000, D0 MOVE.L #%10111010, D1 MOVE.L #\$ACEF,D2 DIVU.L D1,D2 ADD.L D0,D2 NOT.L D2 END \$1000

1. Complete the table below:

| Bits of operation | Data size | Postfix | Sample<br>instruction | Underline the affected Hex Digit |

|-------------------|-----------|---------|-----------------------|----------------------------------|

| 32                | Longword  |         |                       | XXXXXXXX                         |

| 16                |           |         | MOVE.W                | XXXX XXXX                        |

| 8                 |           | .В      |                       | XXXXX XXXX                       |

2. State the value of D1 and D2 after execution for each line

| 1. | MOVE.B #7, D1   | D1=\$ |      |

|----|-----------------|-------|------|

| 2. | ADD.B #6, D1    | D1=5  |      |

| 3. | MOVE.W #352, D2 | D2=?  |      |

| 4. | ADD.W D1,D2     | D1=5  | D2=? |

- 1. Given the value D1=0000CAFE and D2 = FFFF1222

- i. Calculate the value OR.B D2,D1

ii. Calculate the value of NOT.W D2

- 2. Given the value D1 = ABBBBB12 AND D2=ACCC1251

- i. Calculate the value AND.B D2,D1

ii. Calculate the value MOVE.W D1,D2

- 3. Given the value, D1 = 0000 FFFE and D2 = ABCD 1234.

- a) Calculate the value of OR.B D2, D1

- b) Calculate the value of ADD.W D2,D1

- 1. Identify the type of addressing mode in the following instruction.

- a. MOVE.B #8,D3

- b. MOVE.W D3,(A1)

- c. MOVE.W \$1900,D2

- d. MOVE.L D1, D0

- 2. Write comment in the below table.

|        | SYNTAX           | COMMENT |

|--------|------------------|---------|

| ORG    | \$6000           |         |

| MOVE.L | #\$FFFF 1234, D0 |         |

| MOVE.B | (A1), D1         |         |

| ADD.W  | D2, D1           |         |

| MULU.W | #\$5D, DO        |         |

| NOT.W  | D2               |         |

| RTS    |                  |         |

- D1 = 11223344 D2=AA69B250

- 1. State The Value Of Register D1 And D2 When The Instruction Below Is Executed:

- i. MOVE.W #\$1235,D1

- ii. MOVE.B D2,D1

- iii. MOVE.B #%10101111,D2

- iv. MOVE.W \$1000,D1 a. 1000 88 b. 1001 55

- v. MOVE.B D2,\$1000

- vi. MOVE.W #77,D1

- vii. MOVE.L #\$ABCD1111,D2

viii. MOVE.W D1,D2

ix. MOVE.W #@34,D1

x. MOVE.B #\$11,D1

2. Calculate the value of the register below after execution :

D1 = \$12122222 D2 = \$12341515

- i. ADD.B D2,D1

- ii. SUB.B D1,D2

iii. ADD.W #@25,D2

iv. MULU.B #2,D1

v. MOVE.B D2,D1

vi. ADD.B D1,D2

3. Write an instruction based on statement below :

| STATEMENT                                                                                                        | INSTRUCTION |

|------------------------------------------------------------------------------------------------------------------|-------------|

| Transfer data from register D2 to register D3 in long size                                                       |             |

| Transfer 101010112 to register D4 in long size                                                                   |             |

| Transfer data from address 5000 to register D2 in byte size                                                      |             |

| Transfer ABCD <sub>16</sub> to register D1 in word size.                                                         |             |

| Sub a data in data register D1 and D2 in word size                                                               |             |

| Add a data in address register A1 and D3 in word size                                                            |             |

| Divide a data in register D3 to register D5 in long size                                                         |             |

| Multiply 458 to data in register D1 in word size                                                                 |             |

| Transfer a data from register D1 to register<br>D3 and add a data in register D3 to<br>register D4 in byte size. |             |

- 1. Write a programme using Assemble language to solve the operation below:

- a) (BACA<sub>16</sub> 1234<sub>16</sub>) + NOT (ADA<sub>16</sub> AND 87<sub>16</sub>)

b) (100<sub>10</sub> AND 20<sub>10</sub>) + (10<sub>10</sub> / A<sub>16</sub>) + NOT FFFF<sub>16</sub>

c) ! ((768 / 10102) | | (ABCD16 && 123416))

2. Write a program that calculate the area of rectangle

3. Write a program that calculate the average of two numbers. The numbers is 56 and 14.

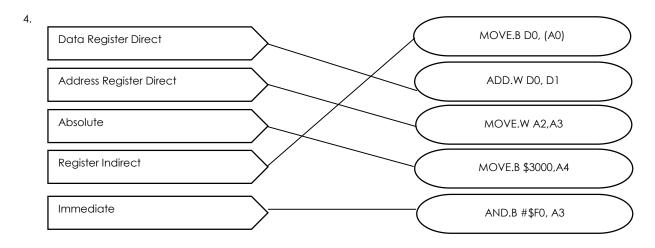

4. Match the following addressing mode with its instruction sets examples

| Data Register Direct    | MOVE.B D0, (A0)  |

|-------------------------|------------------|

| Address Register Direct | ADD.W D0, D1     |

| Absolute                | MOVE.W A2,A3     |

| Register Indirect       | MOVE.B \$3000,A4 |

| Immediate               | AND.B #\$F0, A3  |

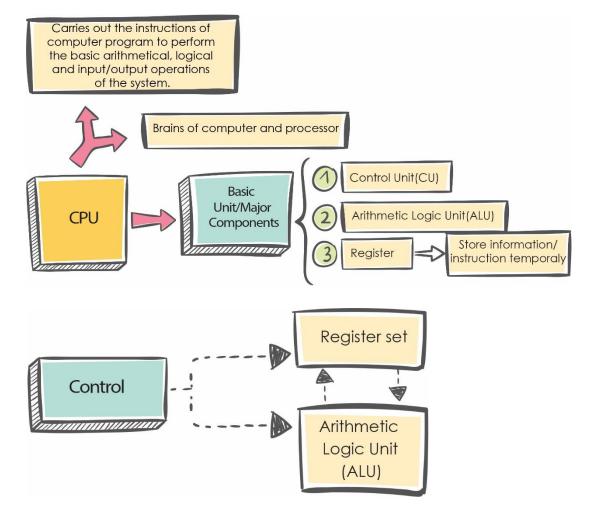

This chapter explains briefly the central processing unit.

# **Topic : The Central Processing Unit**

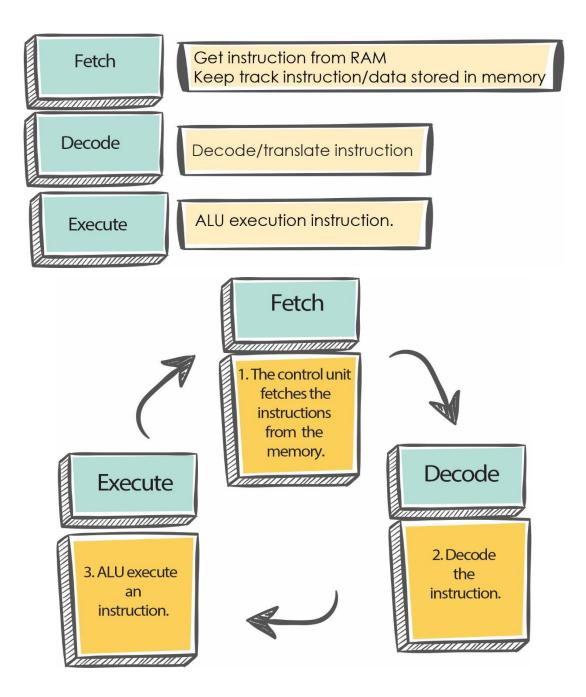

### Instruction Cycle

The instruction cycle is the basic operational process of a computer system. It is the process by which a computer retrieves a program instruction from its memory, determines what actions the instruction describes, and then carries out those actions.

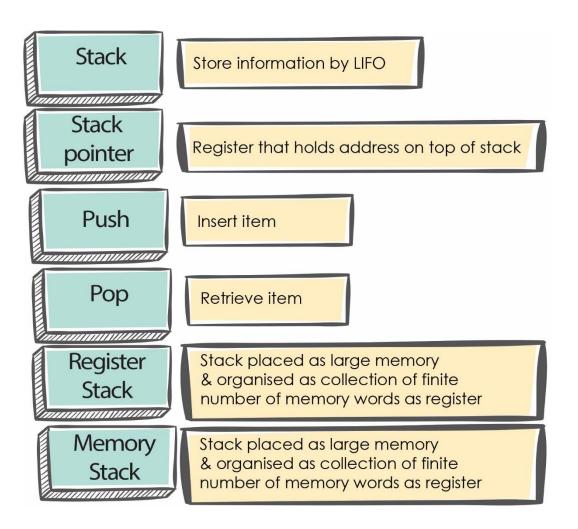

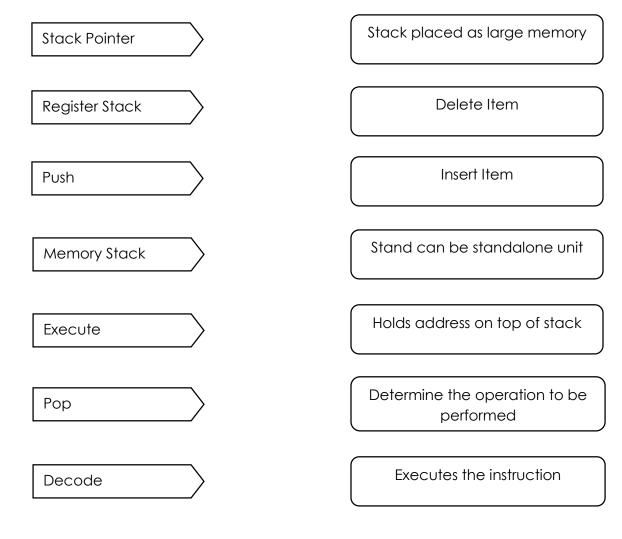

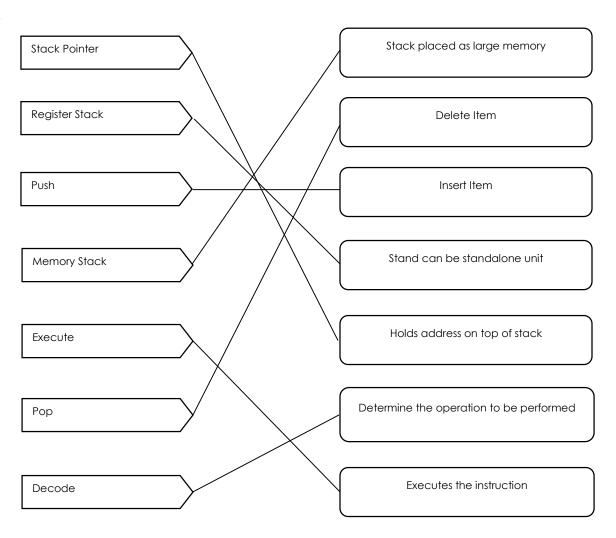

### Stack

- A useful feature that is included in the CPU of most computers.

- A storage device that store information in such a manner that the item stored (in) last, is the first item retrieved (out)/LIFO.

Terminologies in stack :

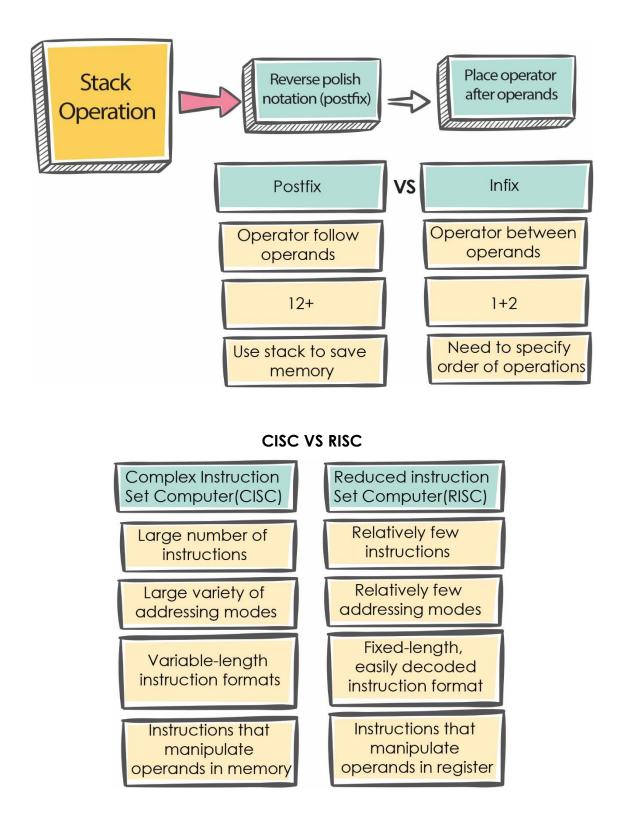

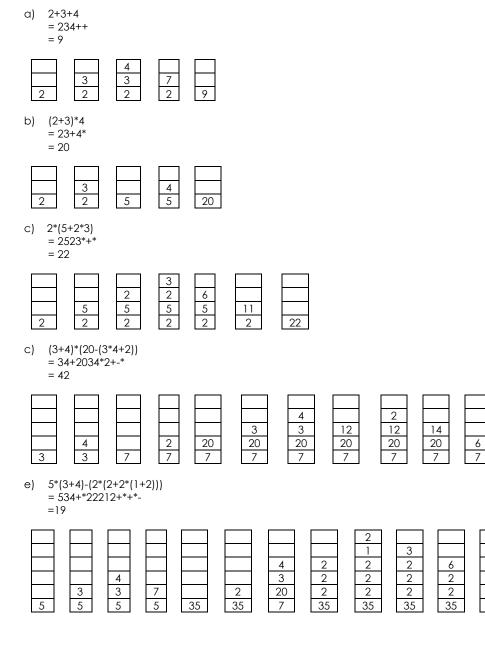

### **Reverse Polish Notation**

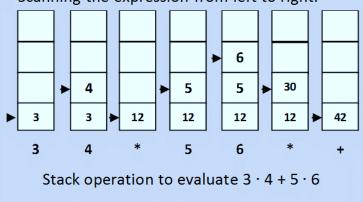

The Polish mathematician *Lukasiewicz* show that arithmetic expression can be represented in prefix notation. This representation often referred to as *Polish notation*; place the operator before the operand. The postfix notation, referred to as reverse Polish notation (RPN), places the operator after the operand.

The reverse Polish notation is in a form suitable for stack manipulation. The expression,

A \* B + C \* D

Is written in reverse Polish Notation as,

AB \* CD \* +

Proceeding from left to right, we first add A and B, then add D and

E. At this point we are left with:

### (A + B)(D + E)C \* F + \*

Where (A + B) and (D + E) are each a single number obtained from the sum. The two operand for next \* are C and (D + E). These two numbers are multiplied and the product added to F. The final \* cause the multiplications of the two terms.